- Cadence Concept-HDL & Allegro原理圖與電路板設計(第2版)

- 周潤景 李茂泉編著

- 764字

- 2021-07-23 18:11:33

3.5 創建附加頁

本節為設計添加一個補充頁,并把第一頁復制到這一頁。

1.復制第一頁

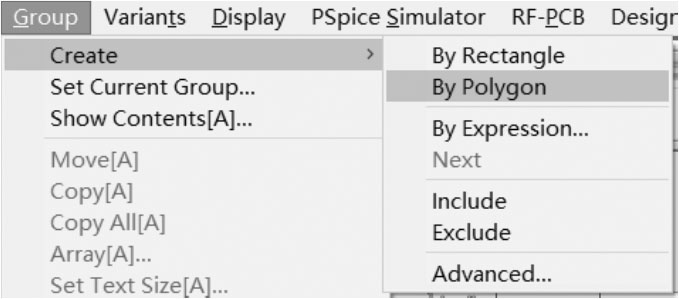

(1)使用Group→Create→By Rectangle或Group→Create→By Polygon指令圈選元件和導線(不要把頁面的邊框起來),如圖3-5-1所示。

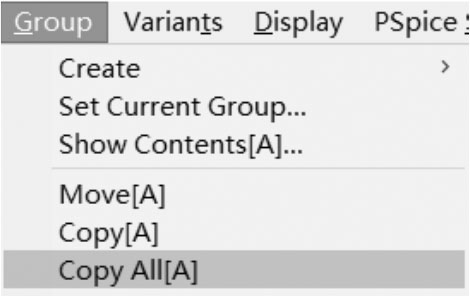

(2)選擇Group→Copy All[A],如圖3-5-2所示。圈選的復制品被放入緩沖器,并跟隨光標移動。

圖3-5-1 菜單欄

圖3-5-2 菜單欄

(3)單擊Add New Page圖標![]() 添加設計的第二頁。

添加設計的第二頁。

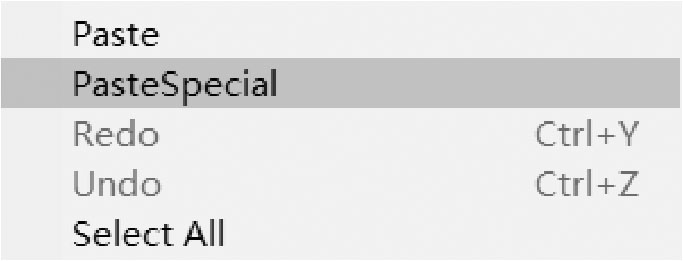

(4)單擊右鍵并從快捷菜單中選擇PasteSpecial,如圖3-5-3所示。

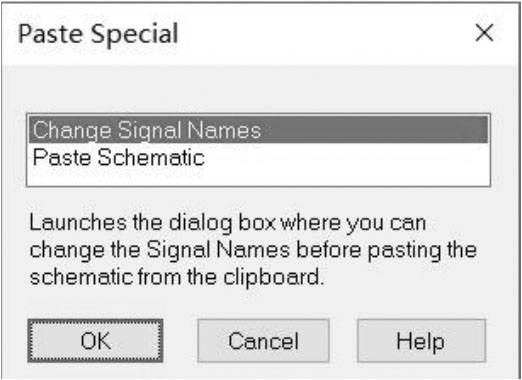

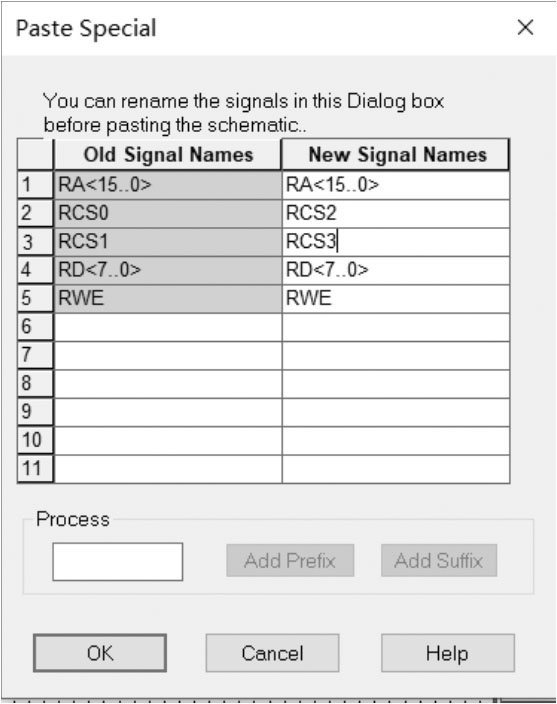

(5)彈出Paste Special窗口,如圖3-5-4所示,單擊Change Signal Names。

圖3-5-3 快捷菜單

圖3-5-4 Paste Special窗口

(6)在Paste Special窗口中,如圖3-5-5所示,更改RCS0為RCS2,更改RCS1為RCS3,單擊OK按鈕。

(7)單擊元件和導線放置在頁面中間的位置,單擊右鍵并選擇Done。

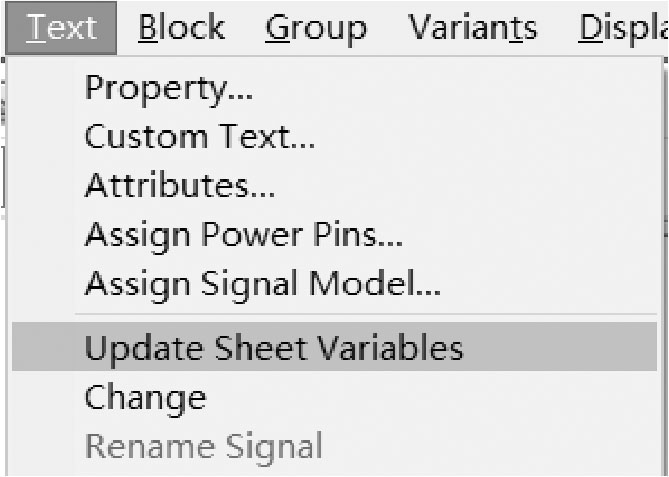

(8)選擇File→Save 和Text→Update Sheet Variables,如圖3-5-6所示。

圖3-5-5 Paste Special窗口

圖3-5-6 菜單欄

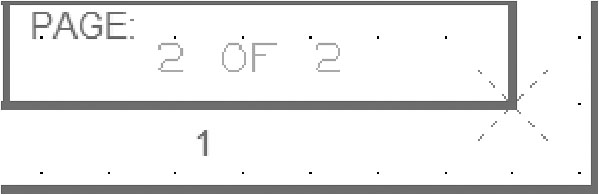

(9)放大標題,注意Page顯示為“2 of 2”,如圖3-5-7所示。

圖3-5-7 標題欄

(10)單擊右鍵并選擇Zoom Fit圖標![]() 。

。

2.添加輸入(inport)/輸出(outport)端口

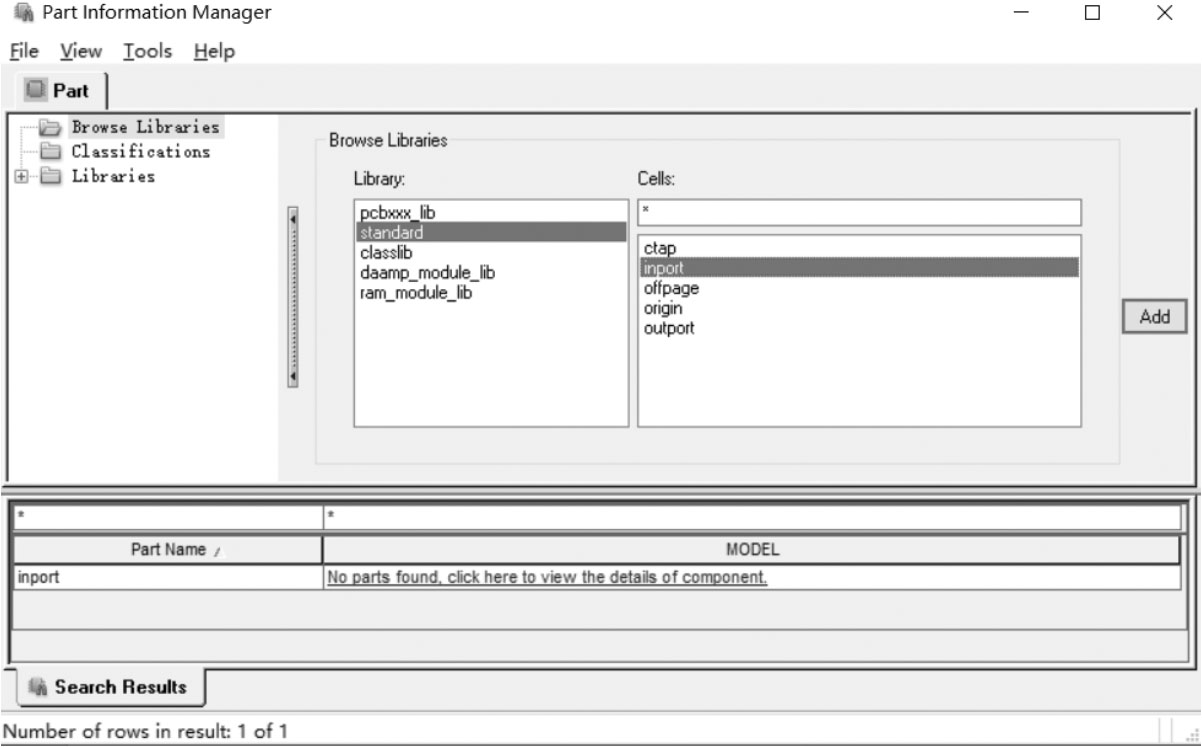

(1)打開Part Information Manager窗口,如圖3-5-8所示,從standard庫添加5個inport,如圖3-5-9所示。輸出端口同理,在standard庫中選擇outport進行添加。

圖3-5-8 Part Information Manager窗口

圖3-5-9 添加輸入端口

(2)選擇File→Save。返回第一頁,添加5個inport到該頁的信號源,然后保存設計。

3.運行打包

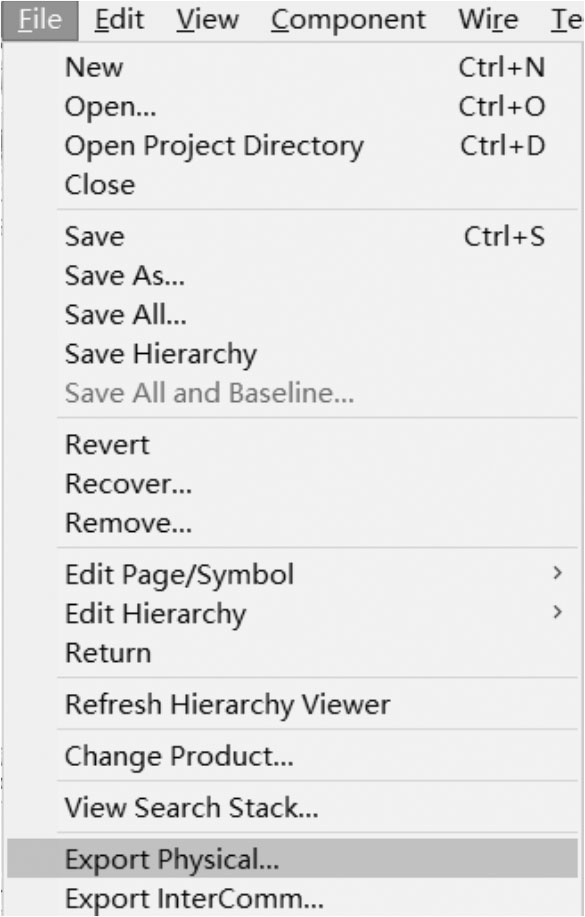

(1)在Design Entry HDL中選擇File→Export Physical,如圖3-5-10所示。

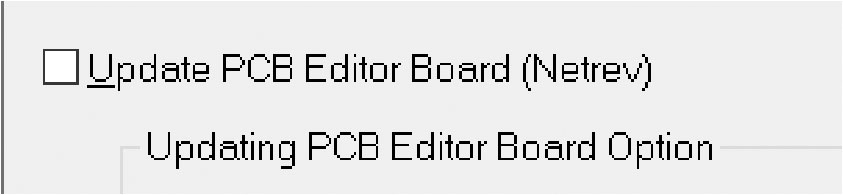

(2)確保Update PCB Editor Board(Netrev)選項未被選中,如圖3-5-11所示。單擊OK按鈕開始打包。

圖3-5-10 菜單欄

圖3-5-11 不選Update PCB Editor Board(Netrev)選項

(3)當打包報告報錯時,單擊Yes按鈕查看詳細文件。

(4)滾動pxl.log文件窗口的底部,注意到錯誤如下:

ERROR(1109):Cannot package instance into package U101.

ERROR(1109):Cannot package instance into package U102.

這個錯誤的發生是因為兩頁中元件標注的賦值相同。

(5)退出報錯文件并關閉Progress窗口。

4.調試打包錯誤

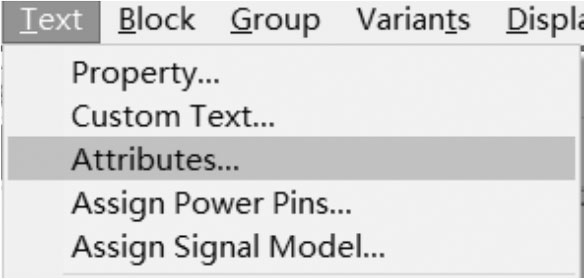

(1)進入第二頁,選擇Text→Attributes,如圖3-5-12所示,單擊元件U101。

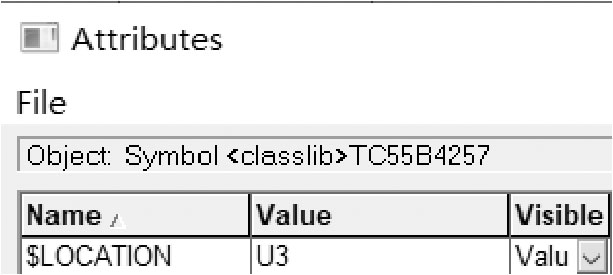

(2)在Attributes窗口,給name的屬性LOCATION前添加一個美元符號($),如圖3-5-13所示。

圖3-5-12 菜單欄

圖3-5-13 Attributes窗口

(3)U102做相同的操作,保存設計。

(4)選擇File→Export Physical,單擊OK按鈕開始打包,打包完成后單擊No按鈕。

- C++程序設計(第3版)

- Spring Cloud Alibaba微服務架構設計與開發實戰

- 數據庫原理及應用(Access版)第3版

- Python入門很簡單

- 精通Python自然語言處理

- Redis Essentials

- JAVA程序設計實驗教程

- Unity Game Development Scripting

- Cocos2d-x學習筆記:完全掌握Lua API與游戲項目開發 (未來書庫)

- 持續輕量級Java EE開發:編寫可測試的代碼

- MINECRAFT編程:使用Python語言玩轉我的世界

- Java EE 7 with GlassFish 4 Application Server

- MyBatis 3源碼深度解析

- ROS機器人編程實戰

- INSTANT PLC Programming with RSLogix 5000