- 基于NI Multisim 11的PLD/PIC/PLC的仿真設計

- 聶典 李北雁等編著

- 549字

- 2019-03-01 13:31:27

2.5 7段譯碼器

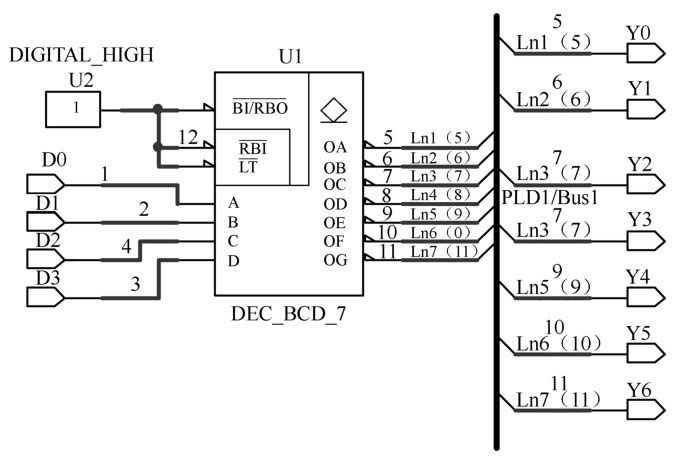

NI Multisim 11中“7段譯碼器”電路如圖1.2.15所示。

圖1.2.15 “7段譯碼器”電路

NI Multisim 11中產生的“7段譯碼器”的VHDL代碼如下所示。

---------------------------------------------------

-- Source File: E:\_uc3300a57fa4e8e~1\_uc34e0a7bc757fa~1\_

uc37b2c4e8c7ae0~1\7_uc26bb58bd1~1.MS1

-- Sheet: 7_uc46bb58bd178015668_1

-- RefDes: PLD1

-- Part Number:

-- Generated By: NI Multisim

--

-- Author: ni

-- Date: Friday, August 27 10:20:10, 2010

---------------------------------------------------

---------------------------------------------------

-- Use: This file defines the top-level of the design

-- Use With File:

---------------------------------------------------

library ieee;

use ieee.std_logic_1164.ALL;

use ieee.numeric_std.ALL;

library work;

use work.7_uc46bb58bd178015668_pkg.ALL;

entity \7_uc_uc46bb58bd178015668_1\ is

port (

D0 : in std_logic;

D1 : in std_logic;

D2 : in std_logic;

D3 : in std_logic;

Y0 : out std_logic;

Y1 : out std_logic;

Y2 : out std_logic;

Y3 : out std_logic;

Y4 : out std_logic;

Y5 : out std_logic;

Y6 : out std_logic

);

end \7_uc_uc46bb58bd178015668_1\;

architecture behavioral of \7_uc_uc46bb58bd178015668_1\ is

component AUTO_IBUF

port(

I : in std_logic;

O : out std_logic

);

end component;

component AUTO_OBUF

port(

I : in std_logic;

O : out std_logic

);

end component;

component DEC_BCD_7_NI

port (

A : in STD_LOGIC;

B : in STD_LOGIC;

C : in STD_LOGIC;

D : in STD_LOGIC;

LT : in STD_LOGIC;

RBI : in STD_LOGIC;

BI : in STD_LOGIC;

Y0 : out STD_LOGIC;

Y1 : out STD_LOGIC;

Y2 : out STD_LOGIC;

Y3 : out STD_LOGIC;

Y4 : out STD_LOGIC;

Y5 : out STD_LOGIC;

Y6 : out STD_LOGIC

);

end component;

component DIGITAL_HIGH_NI

Port (

Y: out STD_LOGIC:='1'

);

end component;

signal \1\ : std_logic;

signal \2\ : std_logic;

signal \3\ : std_logic;

signal \4\ : std_logic;

signal \5\ : std_logic;

signal \6\ : std_logic;

signal \7\ : std_logic;

signal \8\ : std_logic;

signal \9\ : std_logic;

signal \10\ : std_logic;

signal \11\ : std_logic;

signal \12\ : std_logic;

begin

U1 : DEC_BCD_7_NI

port map( A => \1\, B => \2\, C => \4\, D => \3\, Y0 => \5\, Y3 => \8\, Y4 => \9\, Y5 => \10\, Y2

=> \7\, Y1 => \6\, Y6 => \11\, LT => \12\, RBI => \12\, BI => \12\ );

D0_AUTOBUF : AUTO_IBUF

port map( I => D0, O => \1\ );

D1_AUTOBUF : AUTO_IBUF

port map( I => D1, O => \2\ );

D2_AUTOBUF : AUTO_IBUF

port map( I => D2, O => \4\ );

D3_AUTOBUF : AUTO_IBUF

port map( I => D3, O => \3\ );

Y0_AUTOBUF : AUTO_OBUF

port map( I => \5\, O => Y0 );

Y1_AUTOBUF : AUTO_OBUF

port map( I => \6\, O => Y1 );

Y2_AUTOBUF : AUTO_OBUF

port map( I => \7\, O => Y2 );

Y3_AUTOBUF : AUTO_OBUF

port map( I => \7\, O => Y3 );

Y4_AUTOBUF : AUTO_OBUF

port map( I => \9\, O => Y4 );

Y5_AUTOBUF : AUTO_OBUF

port map( I => \10\, O => Y5 );

Y6_AUTOBUF : AUTO_OBUF

port map( I => \11\, O => Y6 );

U2 : DIGITAL_HIGH_NI

port map( Y => \12\ );

end behavioral;

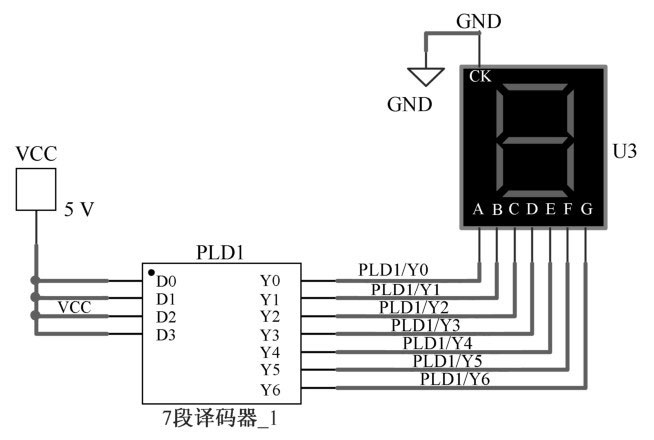

NI Multisim 11中“7段譯碼器”電路的仿真實例如圖1.2.16所示。

圖1.2.16 “7段譯碼器”電路的仿真實例